Synthesis

A State Automata is a DES where the events are all deterministic, this means that we know the sequence of events that will happen, and we can describe how the system will evolve.

NOTE: We do NOT know when the events will happen, the State Automata does not have a concept of time.

A state automata is described by the 5-tuple: ():

- : Event set : .

- : State set : .

- : Domain : Given a state what are the possible events from that state?

- : Transition Function : If at state , event occurs, at which state will I be then?

- : Initial State.

Also if we want to “monitor” one aspect of the system we can use a State Automata with Outputs, described by the 7-tuple: ():

- : Output set : .

- : Transition Function : Given a state , what will be my output ?

State Automata

What do we need for defining the model of a Discrete Event System (DES)?

- Events.

- State.

- Transition Function.

- and it’s domain.

- Initial State.

With these “ingredients” we are ready to introduce the first model class for discrete-event systems:

Graphical representation of state automata:

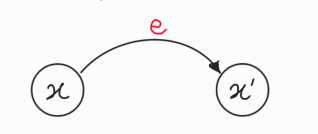

A state automaton (, , , , ) can be represented as a labelled, direct graph where:

- the nodes are the states in .

- there is a direct arc from node to node with label if and only if .

- (, , , ) as defined here.

The initial state is denoted by an arc pointing at the node with no source:

If present, outputs can be represented by labels on the nodes

- there is a label on node if and only if .

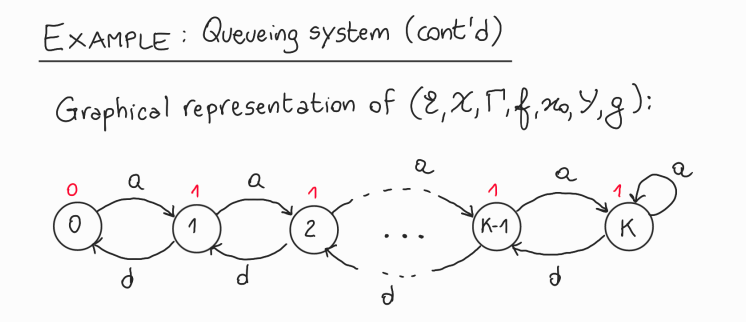

~Example: Queuing system (cont’d):

The system it refers to is given here.

What can we do with these models?

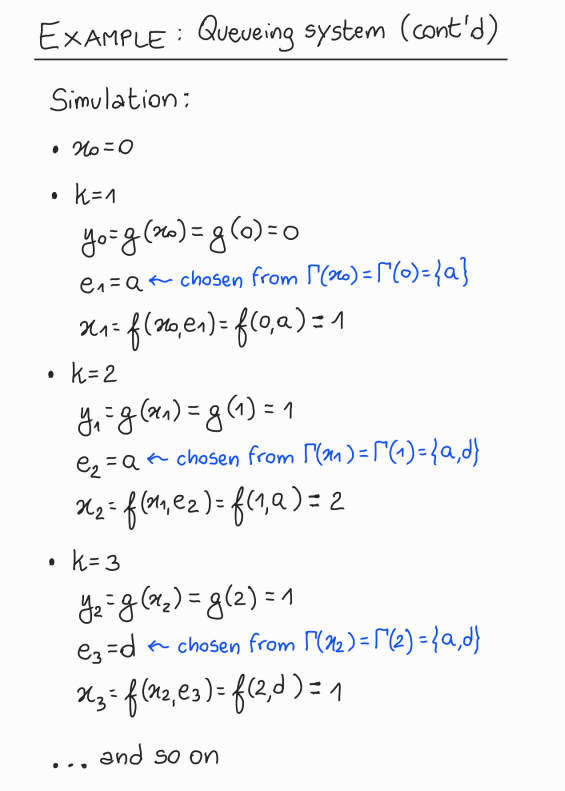

Simulation

State Automata with Output:

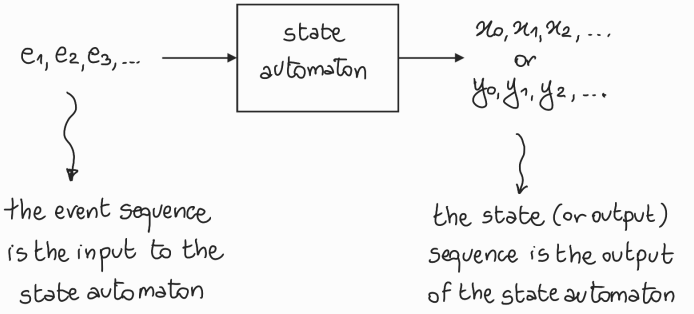

From the input-output point of view, a state automaton can be seen as:

A Purely Logical Model: given an event sequence, it returns the corresponding state (or output) sequence.

- No information about when events (and therefore state transition) occurs

- This is why a state automata are also called logical (or un-timed) models of discrete event systems.

Observation:

For the simulation of a state automaton to not get stuck in a “singularity”, the event sequence provided in input must feasible.